MIPS-Core Application Specific Instruction-Set Processor for IDEA Cryptography - Comparison between Single-Cycle and Multi-Cycle Architectures | DeepAI

What is the difference between a computer that has a 30GHz processor and the other whose performance is 1 MIPS? - Quora

GitHub - bveyseloglu/Single-and-Multi-Cycle-MIPS-CPU-Design: A very simple single cycle and multi cycle MIPS CPU design written in VHDL. The design explained in detail.

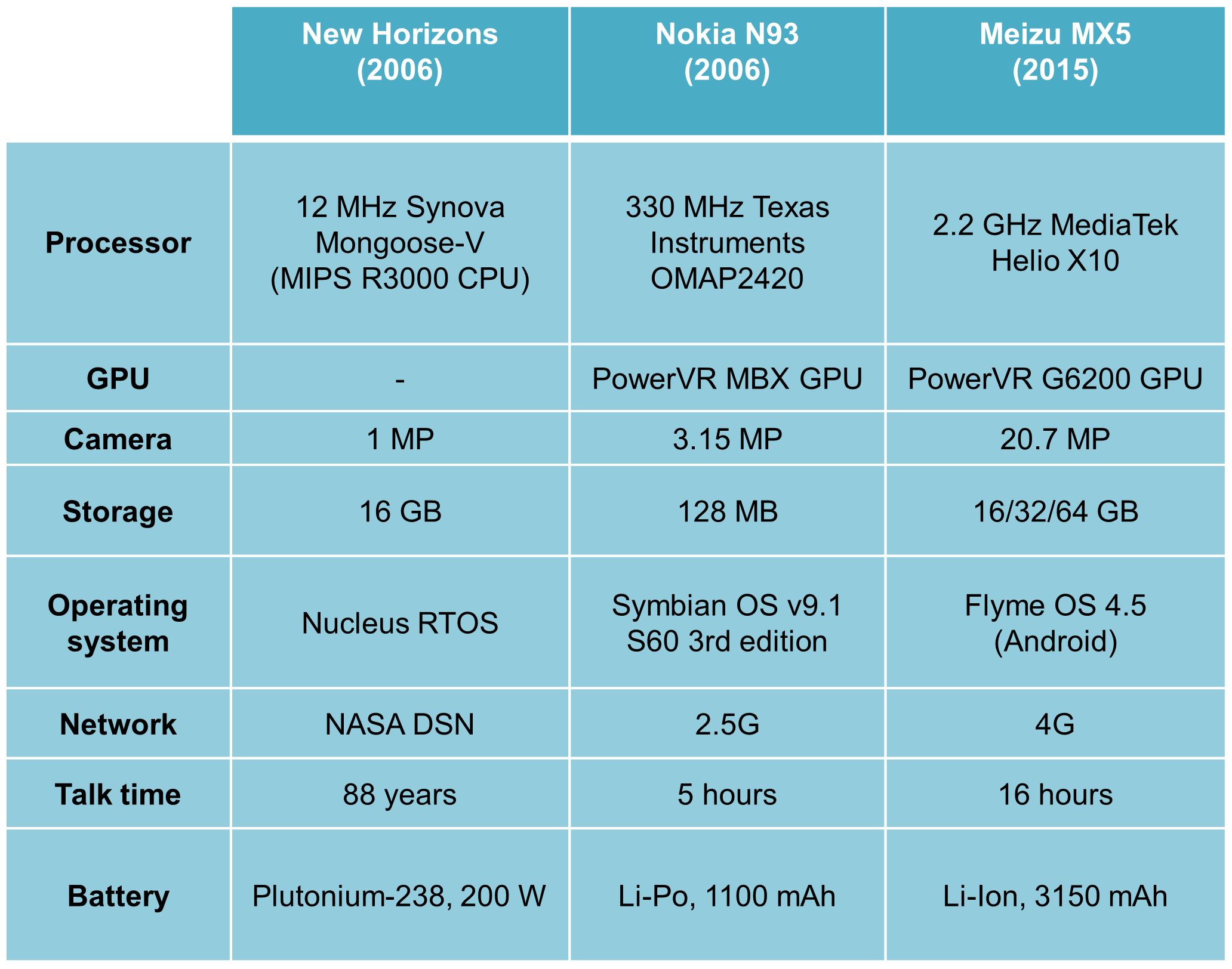

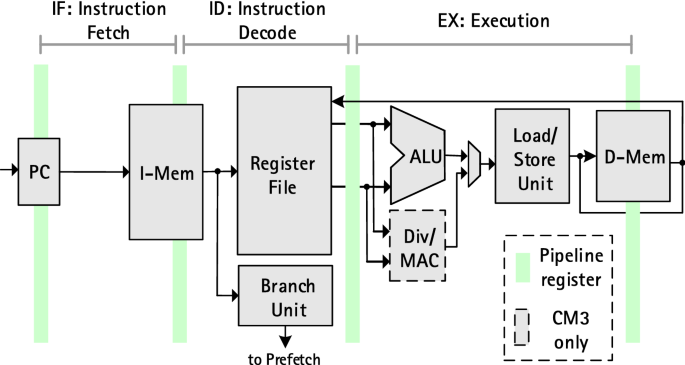

Evaluation of Different Processor Architecture Organizations for On-Site Electronics in Harsh Environments | SpringerLink

The final ISA showdown: Is ARM, x86, or MIPS intrinsically more power efficient? - Architectures and Processors blog - Arm Community blogs - Arm Community

How well is your mainframe outsourcer managing capacity and performance? - Part 2 - Understanding MIPS and MSU - SMT Data

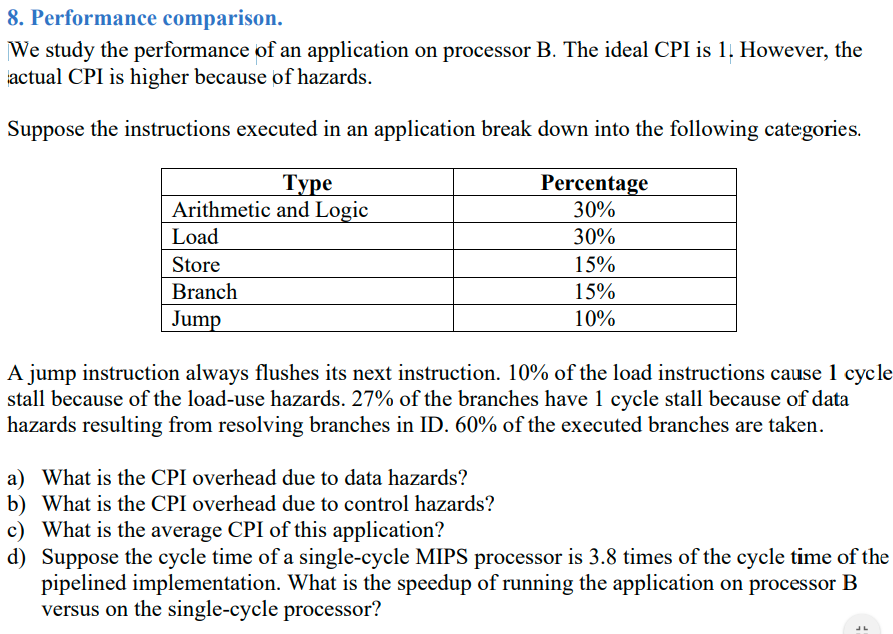

Evaluation of Different Processor Architecture Organizations for On-Site Electronics in Harsh Environments | SpringerLink

The final ISA showdown: Is ARM, x86, or MIPS intrinsically more power efficient? - Architectures and Processors blog - Arm Community blogs - Arm Community

![PDF] MIPS , ARM and SPARC-an Architecture Comparison | Semantic Scholar PDF] MIPS , ARM and SPARC-an Architecture Comparison | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/070e64574ba00314fb49661534e289e3c0664345/3-TableI-1.png)